Ignacio Mártil

Catedrático de Electrónica de la Universidad Complutense de Madrid y miembro de la Real Sociedad Española de Física

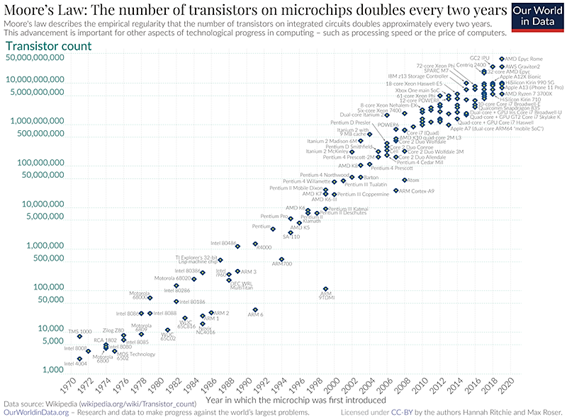

El microprocesador moderno se encuentra entre los sistemas más complejos del mundo, pero en el fondo está constituido por dispositivos que conocemos bien desde hace más de 75 años: el transistor. Como hemos visto en otros artículos publicados en este blog, hoy en día hay miles de millones de ellos en un microprocesador y casi todos son idénticos. Por lo tanto, mejorar su rendimiento y aumentar la densidad de estos transistores es la forma más sencilla de hacer que los microprocesadores y los ordenadores que alimentan funcionen mejor. En esencia, esa es la premisa que está detrás de la Ley de Moore, incluso ahora que parece estar llegando a su final (yo sería muy cauto con los finales, nos dijeron a comienzos de 1980 que el silicio había llegado a su límite...y ahí sigue).

La asombrosa Ley de Moore

Como vimos en un artículo anterior, hacer transistores mejores y más pequeños se está volviendo cada vez más difícil, sin mencionar que es increíblemente costoso. Solo tres empresas, Intel, Samsung y TSMC están equipados para operar en esta frontera de la miniaturización, todos los demás fabricantes de chips se han ido retirando de esta carrera con el paso de los sucesivos nodos tecnológicos. Los tres fabrican circuitos integrados en el equivalente de lo que se llama el nodo de 5 nanómetros, como también vimos en este artículo, en el que tuvimos ocasión de comprobar que ese número ya no tiene un significado físico claro, pero sin embargo refleja el grado en que se miniaturizan los dispositivos de un circuito integrado.

1. ¿Hasta cuándo y hasta donde seguiremos reduciendo el tamaño de los transistores

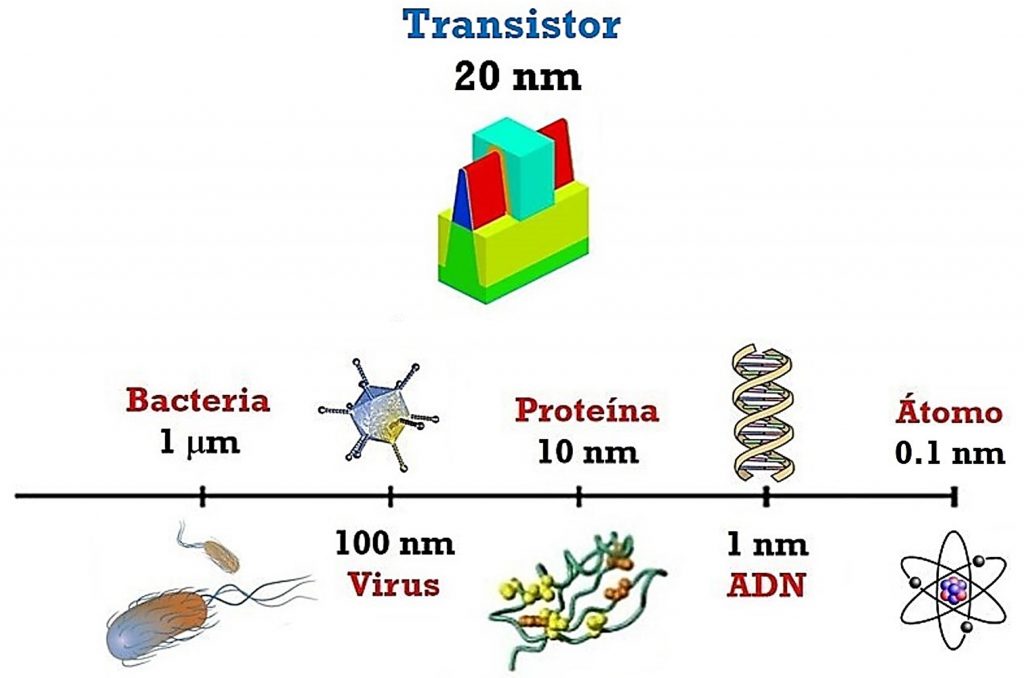

Uno de los problemas que presenta los tamaños tan reducidos que tienen los transistores de ese y otros circuitos equivalentes fabricados en el nodo de 5 nm es que las capacidades del transistor se encuentran auténticamente al límite, unido a algo que es evidente: el escalado no puede continuar para siempre porque los transistores los podemos seguir reduciendo de tamaño, pero hay un límite obvio ¡no pueden ser más pequeños que un átomo!:

Comparando tamaños con la biología. Algunos dispositivos actuales son tan pequeños como una proteína

Eso significa, entre otras cuestiones, que ya no es posible seguir fabricando los transistores "clásicos", puesto que no es posible seguir reduciendo todas las dimensiones sin comprometer de modo irreversible su funcionamiento. Ese límite se conoce en el argot científico como los límites de escalado de los dispositivos MOSFET (Limit of scaling down for FETs).

Ante esto, los retos de la industria son de un calibre inimaginable. Según indica TSMC, el gran fabricante taiwanes, el comienzo de la producción masiva de chips en el nodo de 5 nm comenzó en la primera mitad de 2020. En comparación con la tecnología de 7 nm (el nodo al que sustituye), la tecnología de 5 nm ofrece una mejora de la velocidad de aproximadamente un 15% y una reducción en el consumo de energía de aproximadamente un 30%. Pero esta carrera no parece tener fin, pues ya se están fabricando chips en el nodo de 3 nm desde finales de 2022 (hace no muchos años, Intel pronosticaba que el silicio se acabaría en el nodo de 7 nm. Por ahora, esa previsión no tiene visos de ser cierta).

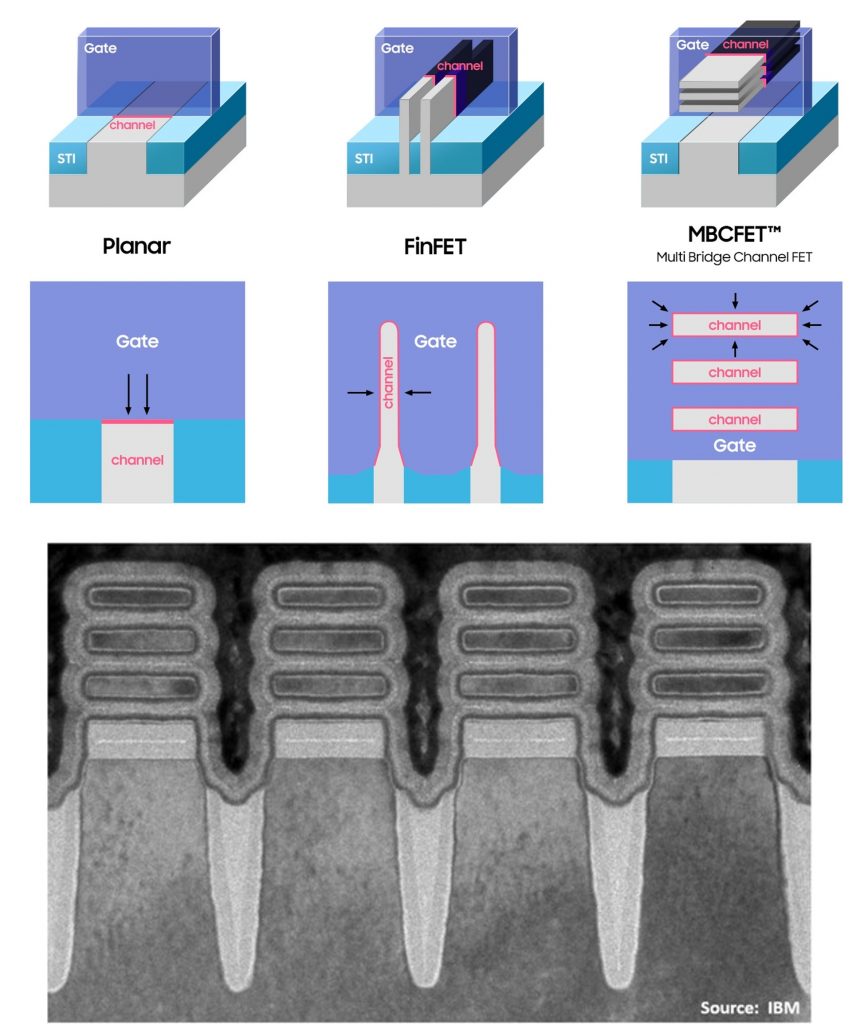

2. ¿Qué tenemos ya en el mercado? El concepto GAAFET

El GAAFET (Gate All Around FET o Transistor de Efecto Campo de Puerta Perimetral o "todo alrededor"), que también se denomina MBCFET (Multi-Bridge Channel FET o Transistor de Efecto Campo de Puerta Múltiple), quizá se convierta en la evolución natural del FinFET [la evolución actual del MOSFET y el dispositivo principal en los chips de los nodos inferiores a 16 nm] y tal vez, serán los dispositivos clave de los chips del inmediato futuro, ya que prometen mayor rendimiento, menor consumo y menos fugas que las que tiene el FinFET. Su diferencia esencial con el FinFET estriba en la posibilidad de transportar más corriente sin aumentar el tamaño del dispositivo y, lo que es crucial, manteniendo reducida su huella en el chip. El siguiente vídeo ilustra el concepto:

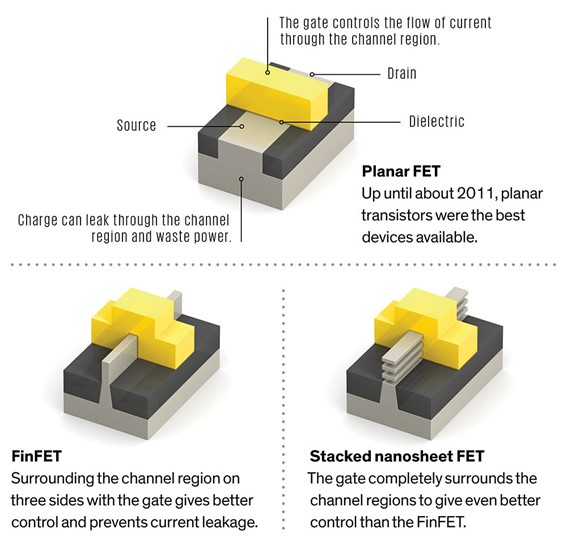

En estos dispositivos la corriente fluye a través de varias capas finísimas de silicio, apiladas una encima de otra, que están completamente rodeadas por el aislante de la puerta del transistor, tal y como muestra la siguiente figura. Este diseño permite reducir las vías de fuga de corriente, facilita un mejor control y un aumento de la corriente que puede conducir el dispositivo. La imagen ilustra las peculiaridades de los tres dispositivos:

Arriba: ilustrando las diferencias entre MOSFET, FinFET y GAAFET. Abajo: imagen tomada al microscopio de un corte transversal de la puerta de un GAAFET. La anchura de cada apilado es del orden de 10 nm.

La siguiente imagen muestra una nueva comparación entre MOSFET, FinFET y GAAFET:

Ilustrando las particularidades de cada dispositivo y como controla cada uno el flujo de corriente a través de la Puerta del transistor

El FinFET sin duda ha sido un gran éxito. Fue introducido comercialmente por primera vez en 2011 en el nodo de 22 nm por Intel y más tarde por Samsung, TSMC y otros. Desde entonces, ha sido el caballo de batalla de los chips de vanguardia de silicio. Pero todo lo bueno llega a su fin. Con el nodo de 3 nm, los FinFET sencillamente ya no están a la altura. Excelente como es, el FinFET también tiene sus problemas: puede conducir más corriente y conmutar más rápido, pero también requiere un proceso de fabricación más complejo y costoso. No entraré en más detalles de cuáles son las razones, pues es verdaderamente complicado tratar de explicarlo con palabras sencillas. Créanme si les digo que no está a la altura de lo que se necesita en el nodo de 3 nm. En todo caso, los FinFET siguen siendo viables para los chips de los nodos comprendidos entre 16 nm y 5 nm, mientras que los transistores planares MOSFET seguirán siendo la tecnología dominante a partir de 22 nm. A modo de resumen y de explicación de las diferencias entre los tres conceptos de FET, este vídeo lo muestra:

Pasar a cualquier nueva tecnología de transistores es un desafío, y el programa de introducción del GAAFET en los chips de vanguardia varía según la empresa que se plantea fabricarlo. Por ejemplo, Samsung está utilizando varios procesos basados en FinFET en los nodos de 7 nm y 5 nm, mientras que ya ha introducido el GAAFET para los chips del nodo de 3 nm en este año. TSMC extenderá el FinFET en sus chips de 3 nm, pero migrará a GAAFET en el nodo de 2 nm en 2024/2025. Intel y otros también están trabajando en GAAFET, pero no hay fecha definida de comercialización, aunque no se debería demorar mucho.

La gran pregunta es cuántas empresas serán capaces de financiar, fabricar y comercializar de manera rentable esta continua reducción de dimensiones. Uno de los responsables de UMC, la otra gran compañía taiwanesa de fabricación de chips, dijo no hace mucho: "Realmente se trata de la economía de la muerte. En los nodos de vanguardia, los costes de las obleas son astronómicos, por lo que muy pocos clientes y muy pocas aplicaciones pueden permitirse aprovechar de manera rentable esta tecnología".

3. Un epílogo que puede durar menos que un suspiro

Sin duda, estas ideas abrirán todo un nuevo mundo en la electrónica. En los próximos años, las dimensiones de los dispositivos se reducirán a muy pocos nanómetros y será prácticamente imposible reducirlas más, lo que parece condenar a su fin a la Ley de Moore y en general, a la era de los circuitos integrados, tal y como los hemos conocido desde su invención, hace más de medio siglo.

Es un hecho que el nodo de la próxima generación será el de 2/3 nm, por lo que pronto nos quedaremos sin nanómetros para nombrar las generaciones de las futuras. Más importante aún, 2 nm es el tamaño de 8 átomos, tan pequeño que podría crear dudas de que el avance de la tecnología de semiconductores se esté acercando a los límites físicos, tal y como he indicado en el párrafo precedente. Sin embargo, la experiencia nos dice que la industria de los semiconductores seguirá progresando, porque todavía hay muchas formas de avanzar en la tecnología de semiconductores más allá de la miniaturización 2-D y también porque la demanda social de sistemas electrónicos cada vez más capaces es insaciable. El ejemplo evidente de esto es al auge de la Inteligencia Artificial, que se sustenta precisamente en los chips más avanzados.

En conclusión, podemos dar por seguro que la creatividad que los ingenieros y diseñadores de estos dispositivos han demostrado durante más de 50 años permitirá "arrebatar la victoria de las fauces de la derrota" ("to snatch victory from the jaws of defeat"). El futuro de la tecnología microelectrónica seguirá deparándonos sorpresas, no tengo la menor duda.

Comentarios

<% if(canWriteComments) { %> <% } %>Comentarios:

<% if(_.allKeys(comments).length > 0) { %> <% _.each(comments, function(comment) { %>-

<% if(comment.user.image) { %>

![<%= comment.user.username %>]() <% } else { %>

<%= comment.user.firstLetter %>

<% } %>

<% } else { %>

<%= comment.user.firstLetter %>

<% } %>

<%= comment.user.username %>

<%= comment.published %>

<%= comment.dateTime %>

<%= comment.text %>

Responder

<% if(_.allKeys(comment.children.models).length > 0) { %>

<% }); %>

<% } else { %>

- No hay comentarios para esta noticia.

<% } %>

Mostrar más comentarios<% _.each(comment.children.models, function(children) { %> <% children = children.toJSON() %>-

<% if(children.user.image) { %>

![<%= children.user.username %>]() <% } else { %>

<%= children.user.firstLetter %>

<% } %>

<% } else { %>

<%= children.user.firstLetter %>

<% } %>

<% if(children.parent.id != comment.id) { %>

en respuesta a <%= children.parent.username %>

<% } %>

<%= children.user.username %>

<%= children.published %>

<%= children.dateTime %>

<%= children.text %>

Responder

<% }); %>

<% } %> <% if(canWriteComments) { %> <% } %>